# 1ch Multi-Standard Analog HD Receiver with MIPI Interface

**PR2000K**

**Rev 0.0**

Last Update: 21. Jun. 2017

6th Floor, 105, Gwanggyo-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, 443-270, Korea TEL +82-31-888-5300 | FAX +82-31-888-5370

Copyright 2017. Pixelplus Co., Ltd. ALL RIGHTS RESERVED

## Product Overview

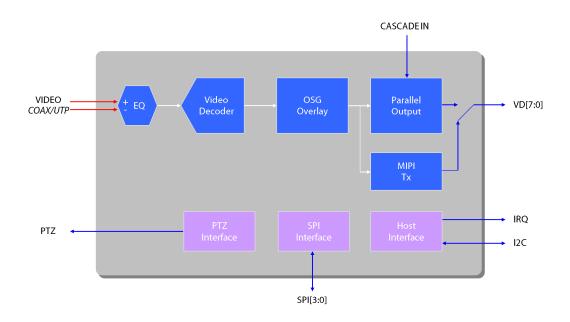

The PR2000 is a HD/SD video receiver which accepts **Any Standard and Resolution of Analog HD/SD video** and guarantees high quality image for **Long-Reach Analog HD** applications. It accepts **Single-ended/Differential** analog HD/SD video signal from camera, then **Cable Equalizer** compensates cable attenuation, and HD/SD video decoder converts analog video signal to digital component data. The PR2000 supports 8bit parallel interface with BT1120/BT656 standard and MIPI-CSI2 interface compliant with MIPI-DPHY v1.0 and MIPI-CSI2 v1.0. The PR2000 also provides **Bi-Directional Coaxial/UTP PTZ** interface so that host can control PTZ camera and receive information from camera with 2-wire serial interface.

# **▶** Features

### **♦** Video Decoder

- $\textcolor{red}{\bigstar} \quad \text{Multi-Standard Analog-HD and SD video with Auto-Detection}$

- All kind of Analog-HD Standard and NTSC/PAL

- $\bigstar$  Any Resolution of Analog-HD and SD video with Auto-Detection

- 1080p25/30, 720p25/30/50/60, 960p25/30/50/60, 480i60, 576i50

- **★** Superior Cable Equalizer for Long-Reach Analog-HD Application

- ★ Differential Analog Input or Two Single-ended Analog Input with MUX Switch

- ★ Multi-Channel Time-Multiplexed Video Output with Dual Edge of Clock

- \* BT1120/BT656 Parallel Output

- **★** MIPI-CSI2 2/4 Data Lane Configuration

- YUV422 8bit Format

- 2/4 Data Lanes for 720p25/30, 4 Data Lanes for 720p50/60, 1080p25/30

### ♦ Bi-Directional PTZ Communication

#### **♦** Graphic Overlay

**★** Dynamic Parking Guide line or OSG Overlay

#### I2C Serial Interface

## **♦** Low Power Consumption

- \* 340mW @ Parallel Output

- \* 268mW @ MIPI Output

#### 40 eQFN (5mm x 5mm) Package

[Fig. 1] Functional Block Diagram